Deep-Dive with AI

Search across all available documentation for this part.

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | ADS808Y/250G4 |

|---|---|

| Architecture | Pipelined |

| Configuration | S/H-ADC |

| Data Interface | Parallel |

| Input Type | Single Ended, Differential |

| Mounting Type | Surface Mount |

| Number of A/D Converters | 1 |

| Number of Bits | 12 bits |

| Number of Inputs | 1 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 °C |

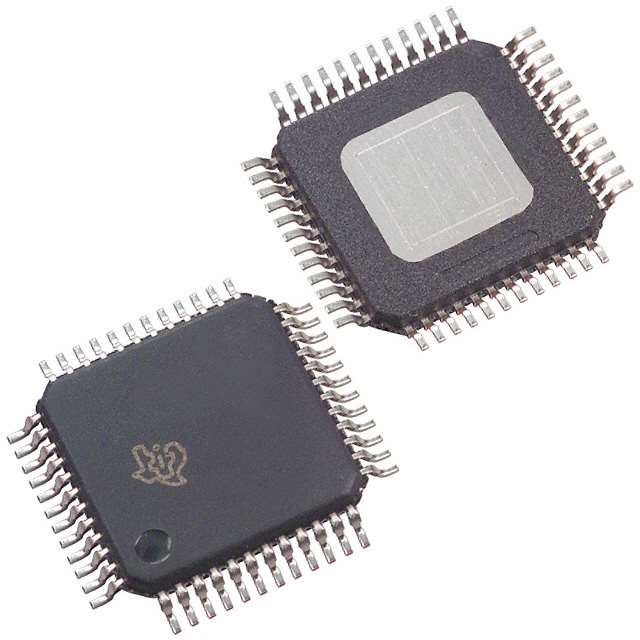

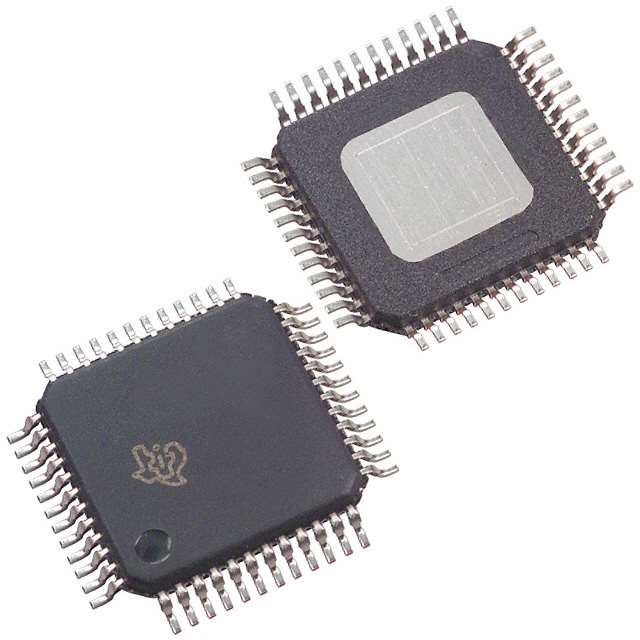

| Package / Case | 48-PowerTQFP |

| Ratio - S/H:ADC | 1:1 |

| Reference Type | External, Internal |

| Supplier Device Package | 48-HTQFP (7x7) |

| Voltage - Supply, Analog | 5 V |

| Voltage - Supply, Digital | 5 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

Description

General part information

ADS808 Series

The ADS808 is a high-dynamic range, 12-bit, 70MHz, pipelined Analog-to-Digital Converter (ADC). It includes a high-bandwidth linear track-and-hold that has a low jitter of only 0.25ps rms, leading to excellent SNR performance. The clock input can accept a low-level differential sine wave or square wave signal down to 0.5Vp-p, further improving the SNR performance. It also accepts a single-ended clock signal and has flexible threshold levels.

The ADS808 has a 2Vp-p differential input range (1Vp-p • 2 inputs) for optimum signal-to-noise ratio. The differential operation gives the lowest even-order harmonic components. A lower input voltage of 1.5Vp-p or 1Vp-p can also be selected using the internal references, further optimizing SFDR. Alternatively, a single-ended input range can be used by tying the IN\ input to the common-mode voltage, if desired.

The ADS808 also provides an over-range flag that indicates when the input signal has exceeded the converter’s full-scale range. This flag can also be used to reduce the gain of the front-end signal conditioning circuitry. It also employs digital error-correction techniques to provide excellent differential linearity for demanding imaging applications. The ADS808 is available in a small TQFP-48 PowerPAD™ thermally enhanced package.

Documents

Technical documentation and resources