ADS54J69 Series

Dual-Channel, 16-Bit, 500-MSPS Analog-to-Digital Converter (ADC)

Manufacturer: Texas Instruments

Catalog

Dual-Channel, 16-Bit, 500-MSPS Analog-to-Digital Converter (ADC)

Key Features

• 16-Bit Resolution, Dual-Channel, 500-MSPS ADCIdle Channel Noise Floor: –159 dBFS/HzSpectral Performance (fIN= 170 MHz at –1 dBFS):SNR: 73 dBFSNSD: –157 dBFS/HzSFDR: 93 dBcSFDR: 94 dBc (Except HD2, HD3, and Interleaving Tone)Spectral Performance (fIN= 310 MHz at –1 dBFS):SNR: 71.7 dBFSNSD: –155.7 dBFS/HzSFDR: 81 dBcSFDR: 94 dBc (Except HD2, HD3, and Interleaving Tone)Channel Isolation: 100 dBc at fIN= 170 MHzInput Full-Scale: 1.9 VPPInput Bandwidth (3 dB): 1.2 GHzOn-Chip DitherIntegrated Decimate-by-2 FilterJESD204B Interface with Subclass 1 Support:1 Lane per ADC at 10.0 Gbps2 Lanes per ADC at 5.0 GbpsSupport for Multi-Chip SynchronizationPower Dissipation: 1.35 W/ch at 500 MSPS72-Pin VQFNP Package (10 mm × 10 mm)16-Bit Resolution, Dual-Channel, 500-MSPS ADCIdle Channel Noise Floor: –159 dBFS/HzSpectral Performance (fIN= 170 MHz at –1 dBFS):SNR: 73 dBFSNSD: –157 dBFS/HzSFDR: 93 dBcSFDR: 94 dBc (Except HD2, HD3, and Interleaving Tone)Spectral Performance (fIN= 310 MHz at –1 dBFS):SNR: 71.7 dBFSNSD: –155.7 dBFS/HzSFDR: 81 dBcSFDR: 94 dBc (Except HD2, HD3, and Interleaving Tone)Channel Isolation: 100 dBc at fIN= 170 MHzInput Full-Scale: 1.9 VPPInput Bandwidth (3 dB): 1.2 GHzOn-Chip DitherIntegrated Decimate-by-2 FilterJESD204B Interface with Subclass 1 Support:1 Lane per ADC at 10.0 Gbps2 Lanes per ADC at 5.0 GbpsSupport for Multi-Chip SynchronizationPower Dissipation: 1.35 W/ch at 500 MSPS72-Pin VQFNP Package (10 mm × 10 mm)

Description

AI

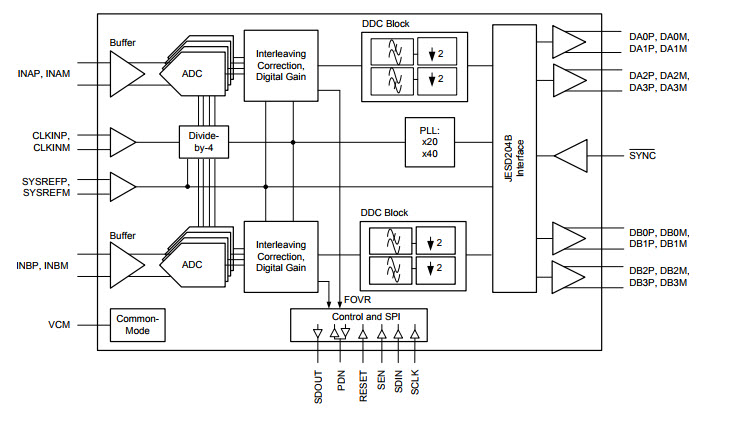

The ADS54J69 is a low-power, wide-bandwidth, 16-bit, 500-MSPS, dual-channel, analog-to-digital converter (ADC). Designed for high signal-to-noise ratio (SNR), the device delivers a noise floor of –159 dBFS/Hz for applications aiming for highest dynamic range over a wide instantaneous bandwidth. The device supports the JESD204B serial interface with data rates up to 10.0 Gbps, supporting one or two lanes per ADC. The buffered analog input provides uniform input impedance across a wide frequency range and minimizes sample-and-hold glitch energy. Each ADC channel is directly connected to a wideband digital down-converter (DDC) block. The ADS54J69 provides excellent spurious-free dynamic range (SFDR) over a large input frequency range with very low power consumption.

The JESD204B interface reduces the number of interface lines, allowing high system integration density. An internal phase-locked loop (PLL) multiplies the ADC sampling clock to derive the bit clock that is used to serialize the 16-bit data from each channel.

The ADS54J69 is a low-power, wide-bandwidth, 16-bit, 500-MSPS, dual-channel, analog-to-digital converter (ADC). Designed for high signal-to-noise ratio (SNR), the device delivers a noise floor of –159 dBFS/Hz for applications aiming for highest dynamic range over a wide instantaneous bandwidth. The device supports the JESD204B serial interface with data rates up to 10.0 Gbps, supporting one or two lanes per ADC. The buffered analog input provides uniform input impedance across a wide frequency range and minimizes sample-and-hold glitch energy. Each ADC channel is directly connected to a wideband digital down-converter (DDC) block. The ADS54J69 provides excellent spurious-free dynamic range (SFDR) over a large input frequency range with very low power consumption.

The JESD204B interface reduces the number of interface lines, allowing high system integration density. An internal phase-locked loop (PLL) multiplies the ADC sampling clock to derive the bit clock that is used to serialize the 16-bit data from each channel.