Catalog

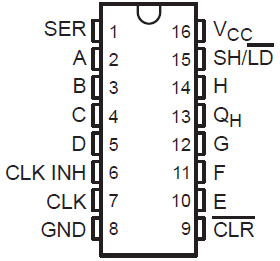

8-Bit Parallel-Load Shift Registers

Key Features

• Operation of 2 V to 5.5 V VCCMax tpdof 10.5 ns at 5 VTypical VOLP(Output Ground Bounce) < 0.8 V at VCC= 3.3 V, TA= 25°CTypical VOHV(Output VOHUndershoot) 2.3 V at VCC= 3.3 V, TA= 25°CIoffsupports partial-power-down-mode operationSynchronous loadDirect overriding clearParallel-to-serial conversionLatch-up performance exceeds 100 mA per JESD 78, Class IIOperation of 2 V to 5.5 V VCCMax tpdof 10.5 ns at 5 VTypical VOLP(Output Ground Bounce) < 0.8 V at VCC= 3.3 V, TA= 25°CTypical VOHV(Output VOHUndershoot) 2.3 V at VCC= 3.3 V, TA= 25°CIoffsupports partial-power-down-mode operationSynchronous loadDirect overriding clearParallel-to-serial conversionLatch-up performance exceeds 100 mA per JESD 78, Class II

Description

AI

The ’LV166A devices are 8-bit parallel-load shift registers, designed for 2 V to 5.5 V VCCoperation.

The ’LV166A devices are 8-bit parallel-load shift registers, designed for 2 V to 5.5 V VCCoperation.