CAHCT138 Series

Automotive Catalog 3-Line to 8-Line Decoders/Demultiplexers

Manufacturer: Texas Instruments

Catalog

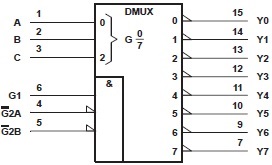

Automotive Catalog 3-Line to 8-Line Decoders/Demultiplexers

Key Features

• Qualified for Automotive ApplicationsEPIC (Enhanced-Performance Implanted CMOS) ProcessInputs Are TTL-Voltage CompatibleDesigned Specifically for High-Speed Memory Decoders and Data-Transmission SystemsIncorporates Three Enable Inputs to Simplify Cascading and/or Data ReceptionLatch-Up Performance Exceeds 250mA Per JESD 17ESD Protection Exceeds 2000V Per MIL-STD-833, Method 3015Qualified for Automotive ApplicationsEPIC (Enhanced-Performance Implanted CMOS) ProcessInputs Are TTL-Voltage CompatibleDesigned Specifically for High-Speed Memory Decoders and Data-Transmission SystemsIncorporates Three Enable Inputs to Simplify Cascading and/or Data ReceptionLatch-Up Performance Exceeds 250mA Per JESD 17ESD Protection Exceeds 2000V Per MIL-STD-833, Method 3015

Description

AI

The SN74AHCT138Q 3-line to 8-line decoder/demultiplexer is designed to be used in high-performance memory-decoding and data-routing applications that require very short propagation-delay times. In high-performance memory systems, this decoder can be used to minimize the effects of system decoding. When employed with high-speed memories utilizing a fast enable circuit, the delay times of this decoder and the enable time of the memory usually are less than the typical access time of the memory. This means that the effective system delay introduced by the decoder is negligible.

The SN74AHCT138Q 3-line to 8-line decoder/demultiplexer is designed to be used in high-performance memory-decoding and data-routing applications that require very short propagation-delay times. In high-performance memory systems, this decoder can be used to minimize the effects of system decoding. When employed with high-speed memories utilizing a fast enable circuit, the delay times of this decoder and the enable time of the memory usually are less than the typical access time of the memory. This means that the effective system delay introduced by the decoder is negligible.